您的位置:主页 > 公告动态 > 正大动态 > 正大动态

晶圆级扇出型先进封装企业「晶通科技」获得数

9月20日消息,杭州晶通科技有限公司(以下简称“晶通科技”)近日宣布完成数千万元A轮融资,本轮融资由水木梧桐创投、天虫资本、春阳资本共同参与,独木资本任公司长期独家融资顾问。资金将重点用于晶圆级扇出型(fan-out)和chiplet产品研发、厂房设备、市场扩展等。公司的二期产线同步寻求地方落地中。

晶通科技成立于2018年,总部位于杭州,是国内领先的以晶圆级扇出型(fan-out)先进封装技术为平台的Chiplet integration方案商,为客户提供从系统集成的设计仿真到晶圆级中道封测的一站式解决方案。公司一期产线坐落于江苏省高邮市,于2023年1月正式通线,同年8月迅速实现批量量产,年产能超12万片。公司主要产品类型包括单芯片Fan-out封装、多芯片Fan-out SIP集成封装、Fan-out POP堆叠封装、多芯片Fan-out混合封装等,场景适用于超高密度封装的大算力芯片(GPU、FPGA)和手机AP、中高密度扇出封装(手环手表、AR/VR、医疗及军工等消费电子SOC),以及低密度的封装(PMIC、WIFI、BB及毫米波等的单芯片扇出、多芯片FoSiP扇出)。

5G通讯爆发时代,电子产品向便携式小型化、高性能、低功耗、高信号强度方向发展,传统的封装方式已不能满足后续主流芯片的需求。先进封装成为延续摩尔定律的重要途径,在提升芯片及模组的高密度高速集成、降低芯片总体成本方面起到引领行业进步的关键性作用。先进封装要求在晶圆划片前融入封装工艺,涉及与晶圆制造相似的光刻、显影、刻蚀、剥离等工序步骤,属于晶圆制造与封测前后道制程间的中道区域。

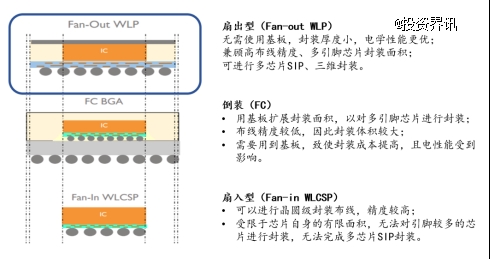

晶圆级扇出型封装(FOWLP),是近年最受关注的先进封装方向之一,其重布线工艺延伸芯片触点到芯片以外的区域来扩展封装可用范围,通过加工更多的I/O数目,获得更高的集成度、更短的线路传输距离以及更好的可靠性能,后期产品扩展方式更灵活。其具体优势包括:(1)互连密度最大化,满足高端大算力芯片封装需求;(2)相较于倒装封装,扇出型封装无需昂贵的载板,成本更低;(3)高集成度,封装后芯片更小更薄并拥有更好的电气属性,能够提供更好的散热性能;(4)Fan-out封装良率更高,切割难度降低;(5)工艺流程更短,更简单,节约成本和生产周期。

同时,Chiplet作为应对摩尔定律放缓而演进出的更高级的系统级封装,通过把原有的单芯片拆解成不同节点的小芯片并封装集成,解决芯片成本效能方面存在的问题。Fan-out作为先进封装中最领先、应用最广泛的技术之一,也是Chiplet集成方案重要的平台基础。

根据Yole数据,2022年全球先进封装市场规模为443亿美元,到2028年预计786亿美元,合计复合增长率为10.6%。先进封装市场规模在整体封装市场规模中的占比由2022年约47%,攀升为2028年的58%。2022年全球扇出型封装市场规模为18.6亿美元,占先进封装市场6.3%份额,预计到2028年其复合年增长率将达到12.5%,达到38亿美元。

公司的技术团队在晶圆级先进封装领域有着丰富的经验和深厚的积累,管理团队均来自应用材料、格罗方徳、日月光、安靠等全球顶尖大厂。核心团队成员在应用材料和国际先进封装研发中心有着十年以上的默契合作,曾主导完成我国首个扇出型02专项,也是国内最早布局和研究chiplet的团队之一。公司董事长、国家半导体行业协会专家委员会主任严晓浪对晶通的研发能力非常看好。

晶通科技具备丰富的先进封装方案设计、仿真验证、工艺开发、产线管理的核心knowhow,经过在核心制程、工艺、设备、耗材等层面的长期研发投入,成功解决了产品在翘曲、位移、重构晶圆、超高密度等方面的难度挑战,是国内鲜有的同时掌握晶圆级fan-out和Chiplet方案的集合体。目前公司已在Fan-out和Chiplet领域布局完整专利,在芯片设计选型、模组的功能实现等方面为客户提供国际领先水准的定制封装方案。现阶段晶通已经可完成2到5微米区间的扇出型封装,正式向全球最顶尖的手机处理器技术看齐。

下一篇:一汽「甩卖」奥迪?